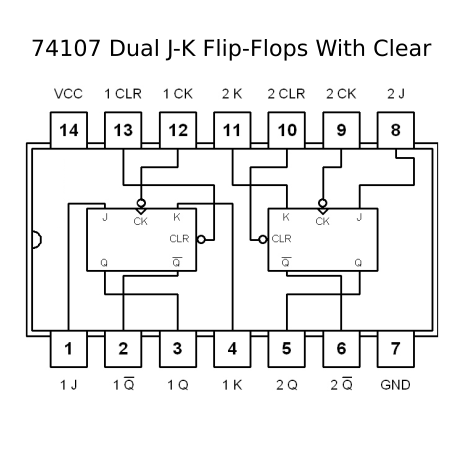

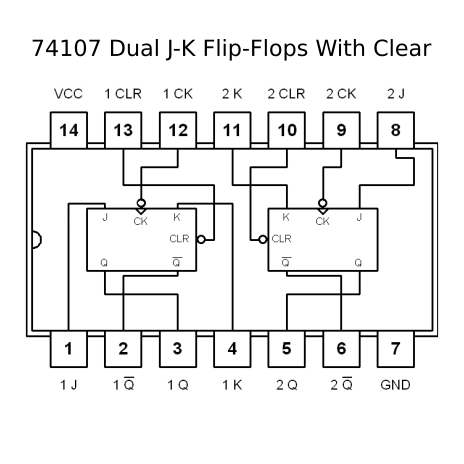

74107 IC Dual JK Flip-Flop with Clear DIP-14

The IC 74107 contains two independent JK flip-flops with independent Clear inputs and shared clock functionality. These flip-flops are positive-edge triggered, meaning they respond to the rising edge of the clock signal. The asynchronous Clear input sets the output to LOW regardless of the clock or data inputs when activated.

Each flip-flop in the 74107 has standard J, K, Clock (CP), and Clear (CLR) inputs, along with complementary outputs Q and Q̅. The JK configuration allows the flip-flops to function in set, reset, hold, or toggle modes depending on input conditions.

Engineers use the 74107 for binary counters, frequency dividers, toggle switches, and memory storage circuits. The dual flip-flop design simplifies timing applications where synchronized or edge-triggered toggling is essential.

Key Features

Dual edge-triggered JK flip-flops in one IC

Asynchronous clear input for each flip-flop

Toggle operation when J = K = HIGH

TTL-compatible logic levels

Complementary Q and Q̅ outputs

Stable performance in synchronous systems

DIP-14 or SOIC-14 package available

Applications

Divide input frequency by two in counters

Build binary ripple counters and shift registers

Store single-bit data in memory latches

Toggle digital states using clocked pulses

Generate synchronized pulses in timing circuits

Debounce mechanical switches for logic systems

Implement state machines in control logic

Create clocked logic elements in sequencers

Manage digital signals in automated testing systems

Teach flip-flop behavior in digital logic labs

Specifications Table

| Parameter | Value |

|---|---|

| Logic Family | TTL |

| Function | Dual JK Flip-Flop with Clear |

| Number of Flip-Flops | 2 |

| Inputs per Flip-Flop | J, K, CP (Clock), CLR (Clear) |

| Output per Flip-Flop | Q, Q̅ |

| Trigger Type | Positive-edge |

| Asynchronous Clear | Active LOW |

| Input HIGH Voltage | ≥ 2.0V |

| Input LOW Voltage | ≤ 0.8V |

| Output HIGH Voltage | ≥ 2.4V |

| Output LOW Voltage | ≤ 0.4V ‘ |

| Propagation Delay (CP→Q) | ~20–30 ns |

| Supply Voltage (Vcc) | 4.75V to 5.25V |

| Operating Temperature | 0°C to 70°C |

| Package Type | DIP-14 / SOIC-14 |

| Number of Pins | 14 |